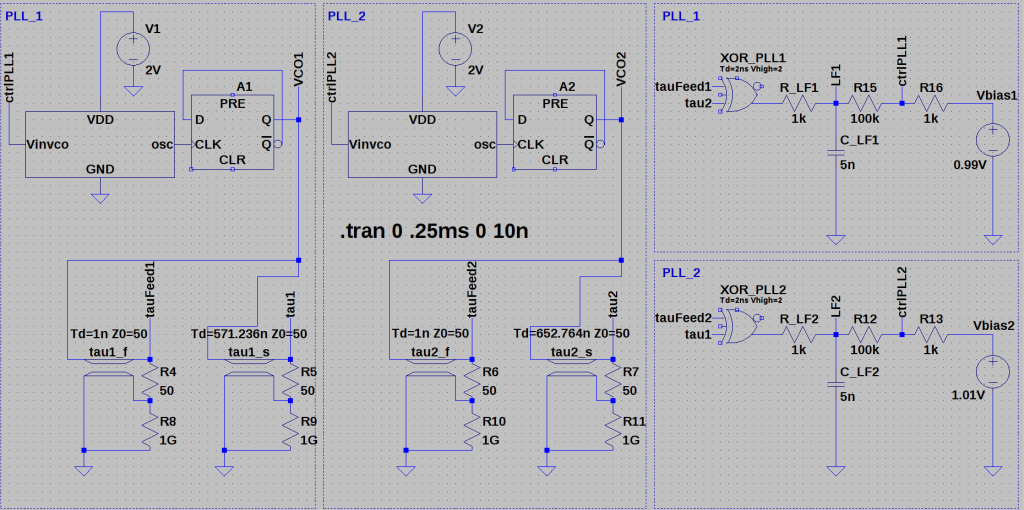

We use LTSpice, an open source analog circuit simulator to simulate systems of coupled DPLL on the level of the voltage and current time-series.

Using this industry-standard approach to test the circuit architectures down to the transistor level before setting up the prototype systems for experimentation allows to identify potential problems such as parasitic resistances and capacitances. We also use it to gain a better intuition on the dynamics within the circuitry as components become heterogeneous and are subject to noise.

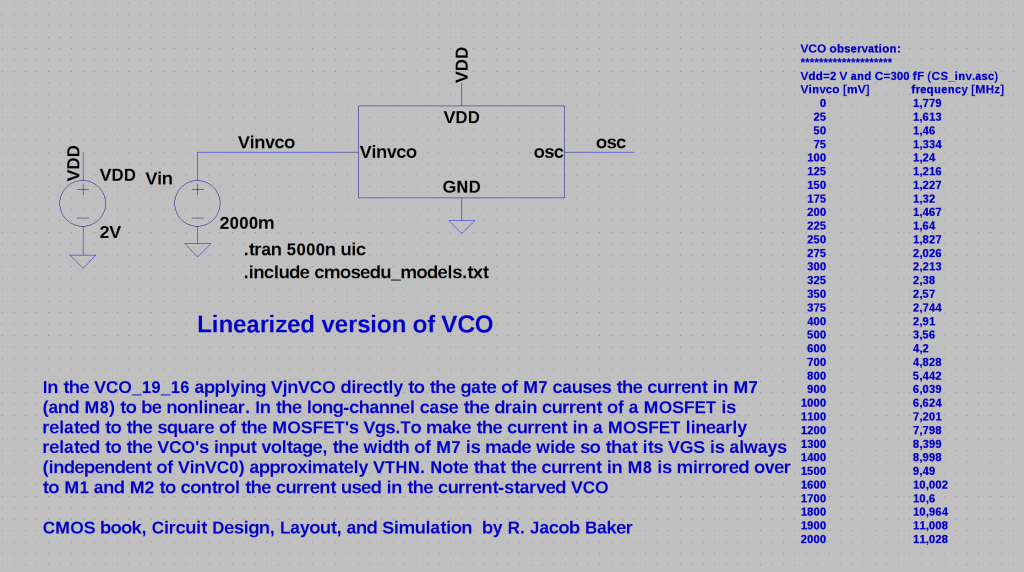

Here we present our current ongoing work on a system of two mutually delay-coupled digital phase-locked loops (DPLLs), each consisting of a phase detector (XOR or flip-flop), a loop filter (first order low pass filter) and an voltage-controlled oscillator (VCO). The VCO is a ring oscillator which is set up from a closed chain of inverter elements, designed by Jacob Baker and available from YOUSPICE.

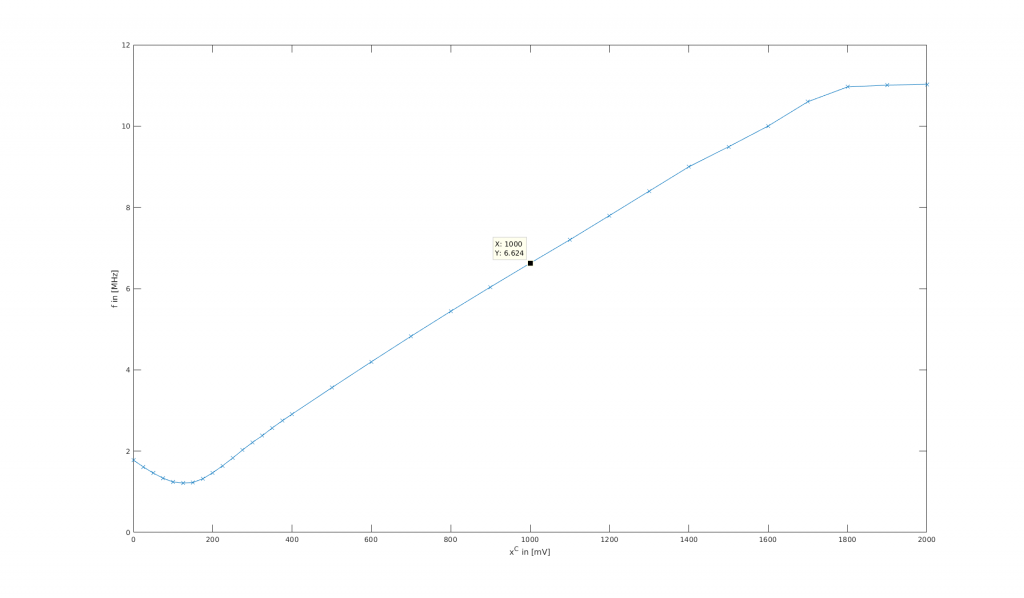

Before going into the details of this circuit, we show the response curve of the VCO plotted against the input voltage at Vinvco. The VCO is supplied by a 2V power source and we changed the parasitic capacitor in the inverter subcircuits of the VCO to ![]() fF.

fF.

.

.